## UNIVERSIDAD CARLOS III DE MADRID DEPARTAMENTO DE INFORMÁTICA GRADO EN INGENIERÍA INFORMÁTICA. ESTRUCTURA DE COMPUTADORES

Para la realización del presente examen se dispondrá de **1:30 horas. NO** se podrán utilizar libros, apuntes **ni** calculadoras de ningún tipo.

## **Ejercicio 1**. Considere el siguiente fragmento en ensamblador:

```

.data

A1: .word 5, 8, 7, 9, 2, 4, 5, 9

A2: .word 1, 4, 3, -8, 5, 6, 5, 9

.align 2

A3: .space 32

.text

```

## Se pide:

- a) ¿Qué representa A1? ¿Cuántos bytes ocupa la estructura de datos A1 (justifique su respuesta)?

- b) Se desea implementar una función cuyo prototipo en un lenguaje de alto nivel es la siguiente:

```

void Mezclar(int a[], int b[], int c[], int N)

```

Esta función recibe 4 parámetros, los tres primeros son vectores de números enteros y el cuarto indica el número de componentes de cada uno de estos vectores. La función se encarga de almacenar en cada componente i de c, el siguiente valor: c[i] = max (a[i], b[i]).

Escriba, utilizando el ensamblador del MIPS32, el código correspondiente a esta función. Utilice para ello la convención de paso de parámetros que se ha descrito a lo largo del curso.

c) Escriba el código necesario para llamar a la función desarrollada en el apartado anterior, para los vectores A1, A2 y A3 definidos en la sección de datos anterior. Asuma que A3 es el vector donde se deben dejar los elementos máximos.

**Ejercicio 2.** ¿Cuál es el número positivo normalizado más pequeño que se puede representar utilizando el estándar de simple precisión IEEE 754. Justifique su respuesta. Indique también el número positivo no normalizado más pequeño que se puede representar. Justifique de igual forma su respuesta.

**Ejercicio 3.** Considere un computador de 32 bits que dispone de un sistema de memoria virtual que emplea páginas de 16 KB y tiene instalada una memoria principal de 1 GB. Indique de forma razonada:

- a) El formato de la dirección virtual.

- b) El número máximo de páginas en este computador.

- c) El número de marcos de página de este computador.

- d) El tamaño del bloque que se transfiere entre disco y memoria principal cuando ocurre un fallo de página

- e) El elemento del computador que genera el fallo de página y quién lo trata.

**Ejercicio 5.** Se dispone de un sistema con una memoria caché de 2 niveles. En la ejecución de una determinada aplicación, la tasa de aciertos de la caché de nivel 1 es del 90% y la tasa de aciertos de la caché de nivel 2 es del 95%. La aplicación genera durante su ejecución un millón de accesos a memoria. Indique de forma razonada:

- a) El número de accesos que se genera a la caché de nivel 1.

- b) El número de accesos que se genera a la caché de nivel 2.

- c) El número de accesos que se genera a memoria principal.

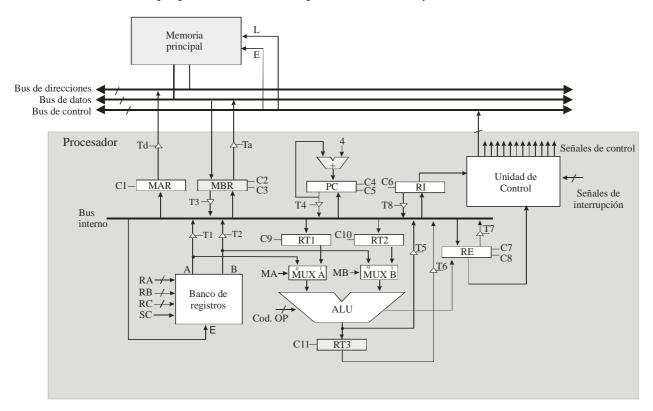

**Ejercicio 6.** Considere el siguiente esquema de procesador de 32 bits. El banco de registros incluye 32 registros. Considere que el computador utiliza un ciclo de reloj para realizar la decodificación de la instrucción y que se conecta a una memoria que permite realizar una operación de lectura y de escritura en un ciclo.

Este computador dispone del juego de instrucciones del MIPS32. Se pide:

- a) Indique las señales de control necesarias para poder realizar la operación elemental RT2 ← R2, donde R2 es el registro número 2 del banco de registros.

- **b)** Indique las operaciones elementales y las señales de control (incluyendo el *fetch*) necesarias para ejecutar la instrucción sw \$t1, 120(\$t2). Explique en primer lugar qué hace esta instrucción.