## **Ejercicios**

1. Dibuje el esquema de transistores de una puerta lógica que realice la función lógica

$$f = \overline{ab(c+d)}$$

- a) en tecnología NMOS

- b) en tecnología CMOS

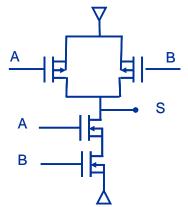

- 2. El circuito que aparece en la figura pertenece a la familia pseudo-NMOS. Responda las siguientes cuestiones:

- a) Indique el tipo de cada transistor.

- Averigüe el estado de cada transistor, en cuanto a si conduce o no (activo/cortado), para cada una de las posibles combinaciones de las señales de entrada A, B y C.

- c) Indique cuál es la función lógica Y que implementa el circuito, a partir de las variables lógicas A, B y C.

- d) Diseñe una puerta CMOS que implemente la misma función lógica.

- e) ¿Qué ventaja(s) piensa que tiene la puerta pseudo-NMOS frente a la CMOS? ¿Y qué desventaja(s)? Razone la respuesta

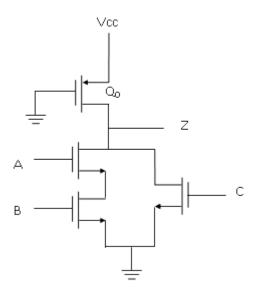

- 3. En la figura se muestra una puerta lógica realizada en tecnología NMOS. Se pide:

- a) Determine la función lógica que realiza el circuito

- b) Dibuje el esquema de transistores de un circuito CMOS que realice la misma función lógica

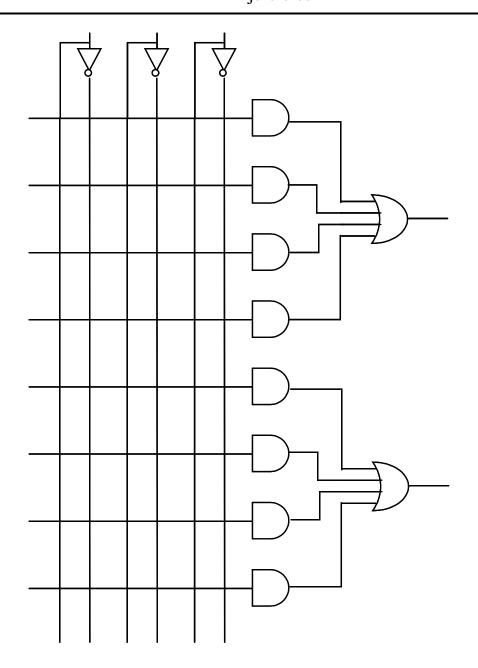

4. Sobre la estructura PAL de la figura, marque con una X las conexiones necesarias para realizar un sumador total.

## **Ejercicios**

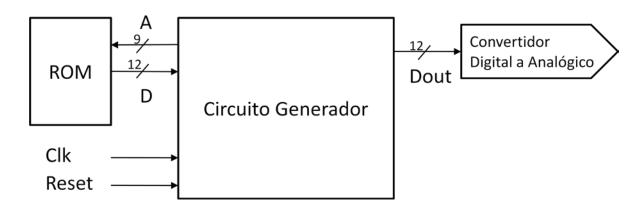

5. Se pretende generar una señal periódica senoidal con un circuito digital y un convertidor Digital/Analógico, como se muestra en la figura. Para ello se dispone una memoria ROM externa de 512x12, en la que se ha almacenado la tabla de la función seno para el primer cuadrante (entre  $0 \text{ y } \pi/2$ ), concretamente

$$2^{10} * Seno(\pi/2 *A/256)$$

$A \in [0, 256]$

siendo A la dirección de memoria ROM.

Nótese que el valor máximo es  $2^{10} = 010000000000$ , el cual se alcanza para A=256. El circuito debe leer la memoria de forma iterativa y generar la salida DOUT periódicamente para los cuatro cuadrantes.

Las entradas y salidas del circuito son las siguientes:

CLK: Señal de reloi

Reset: Señal de inicialización asíncrona A: Dirección de memoria de 9 bits

D: Dato proporcionado por la memoria (12 bits)

DOUT: Dato de salida al conversor en complemento a 2 (12 bits)

### Se pide:

- a) Dibuje un diagrama de bloques del circuito indicando claramente:

- 1. Los componentes utilizados. Puede utilizar cualquiera de los componentes digitales estudiados durante el curso o variaciones de los mismos. **No es necesario implementar los componentes**

- 2. Las señales utilizadas. Describa la función de cada una de ellas

- 3. Si en el circuito utiliza alguna máquina de estados, describa su diagrama

- b) Si el reloj CLK tiene una frecuencia f, ¿cuál será la frecuencia de la señal senoidal generada? Razone cómo modificaría el diseño anterior para permitir que la frecuencia de la señal generada pueda ser variable y configurable externamente.

## **Ejercicios**

### 6. Test

- 1. Entre las memorias RAM:

- a) La DRAM es volátil y la SRAM no.

- a) La DRAM se puede escribir y la SRAM no.

- b) La DRAM requiere refresco dinámico y la SRAM requiere refresco estático.

- c) La DRAM requiere refresco y la SRAM no.

- 2. La última posición de una memoria de 16Kx12 es:

- a) 7FFFH

- b) 3FFFH

- c) 3000H

- d) 8000H

- 3. Una FPGA de SRAM es:

- a) Reprogramable y volátil

- b) Reprogramable, pero no volátil

- c) No reprogramable y volátil

- d) No reprogramable y no volátil

- 4. Una memoria Flash es:

- a) una memoria reprogramable mediante fusibles

- b) una memoria programable por luz UV

- c) una memoria reprogramable electricamente

- d) una memoria no reprogramable

- 5. Un dispositivo lógico programable tipo PAL implementa una suma de productos en la que:

- a) La suma es fija y los productos son programables.

- b) La suma es programable y los productos son fijos.

- c) Tanto la suma como los productos son programables.

- d) Ninguna de las anteriores.

- 6. En una PAL, una salida de polaridad programable

- a) Incorpora un biestable para poder realizar circuitos secuenciales

- b) Incorpora un buffer triestado para utilizar la salida también como entrada

- c) Permite poner el biestable de salida a 0 o a 1

- d) Da más flexibilidad, porque permite negar la salida

- 7. Un dispositivo lógico programable tipo PAL implementa una suma de productos en la que:

- a) La suma es fija y los productos son programables.

- b) La suma es programable y los productos son fijos.

- c) Tanto la suma como los productos son programables.

- d) Ninguna de las anteriores.

## **Ejercicios**

- 8. Los dispositivos programables que tienen mayor capacidad son:

- a) Las PLAs

- b) Los CPLDs de fusibles

- c) Las FPGAs de SRAM

- d) Las FPGAs de antifusibles

- 9. Una LUT es:

- a) Un tipo de memoria RAM

- b) Un tipo de memoria ROM

- c) Una memoria que se utiliza para almacenar la tabla de verdad de una función lógica

- d) Un tipo de dispositivo programable

- 10. Un transistor PMOS (MOSFET tipo P)

- a) Conduce si la tensión de puerta (G) es mayor que la de drenador (D)

- b) Conduce si la tensión de puerta (G) es mayor que la de fuente (S)

- c) Conduce si la tensión de puerta (G) es de nivel alto

- d) Conduce si la tensión de puerta (G) es de nivel bajo

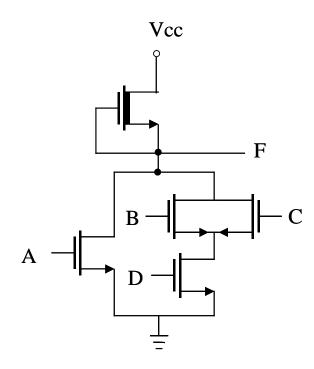

- 11. Señale la puerta lógica que realiza el circuito CMOS de la figura

- a) AND

- b) OR

- c) NAND

- d) NOR

- 12. La tensión de alimentación en un circuito TTL

- a) es de 5V

- b) puede variar entre 1V y 15 V

- c) puede variar entre 15 V y -15 V

- d) depende de V<sub>DD</sub>

- 13. La principal ventaja de un circuito CMOS frente a un circuito TTL es

- a) El circuito CMOS permite mayor tensión de alimentación

- b) El circuito CMOS tiene menor consumo

- c) El circuito CMOS tiene mayor fanout

- d) El circuito CMOS es más barato

- 14. El margen de ruido es:

- a) La diferencia entre la tensión de salida y la tensión de entrada admisible en una puerta lógica

- b) La diferencia entre la tensión de alimentación y la tensión de entrada admisible en una puerta lógica

- c) La diferencia entre la tensión de alimentación y la tensión de salida admisible en una puerta lógica

- d) Ninguna de las anteriores