# ANALYSIS AND DESIGN OF DIGITAL INTEGRATED CIRCUITS AT PHYSICAL LEVEL

Authors: Almudena Lindoso Marta Portela Enrique San Millán Mario García Luis Entrena Celia López

## Outline

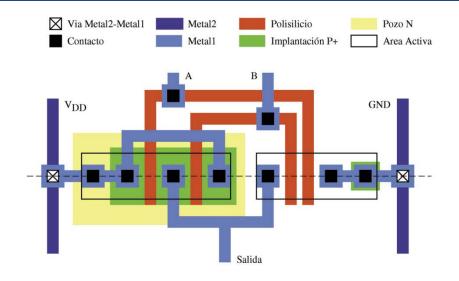

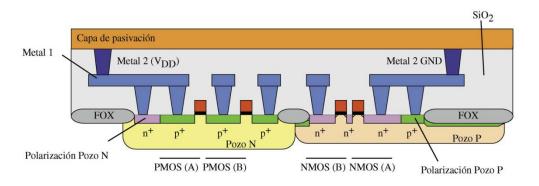

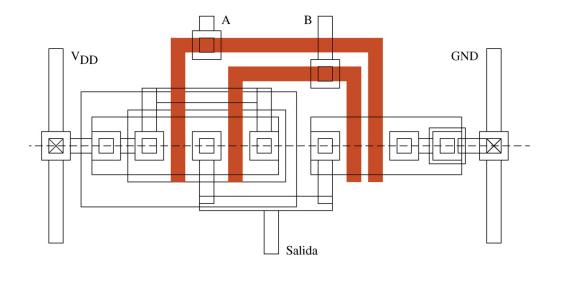

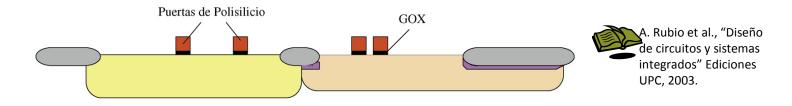

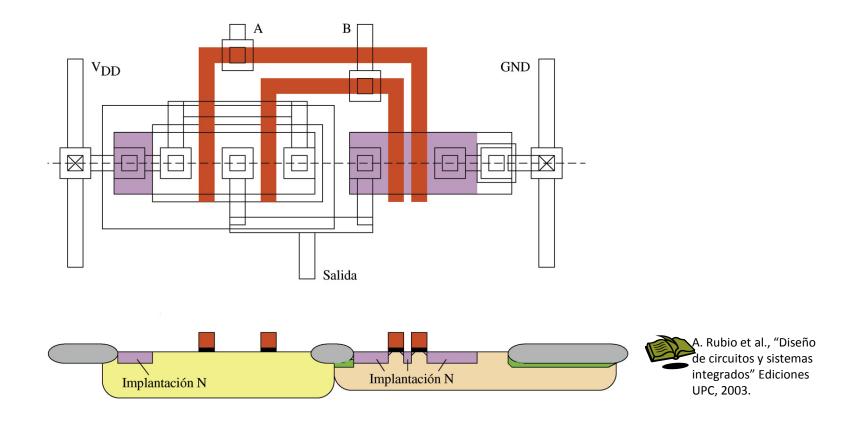

- Required masks for CMOS integrated circuits manufacturing.

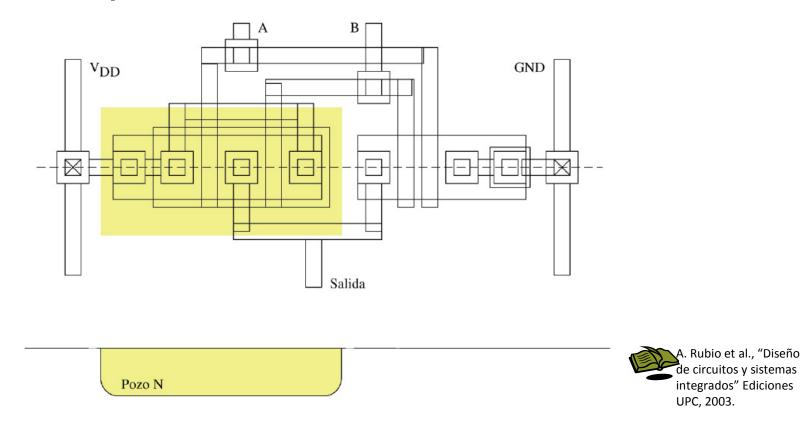

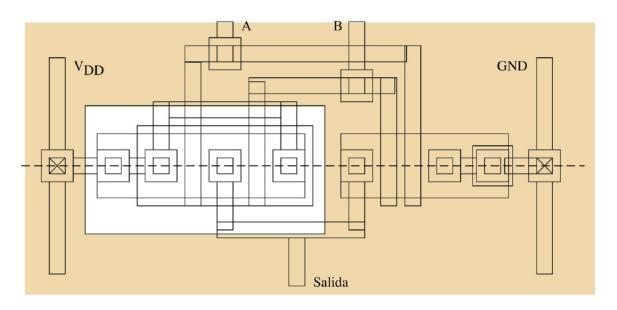

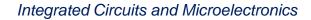

- Layout for a NAND gate

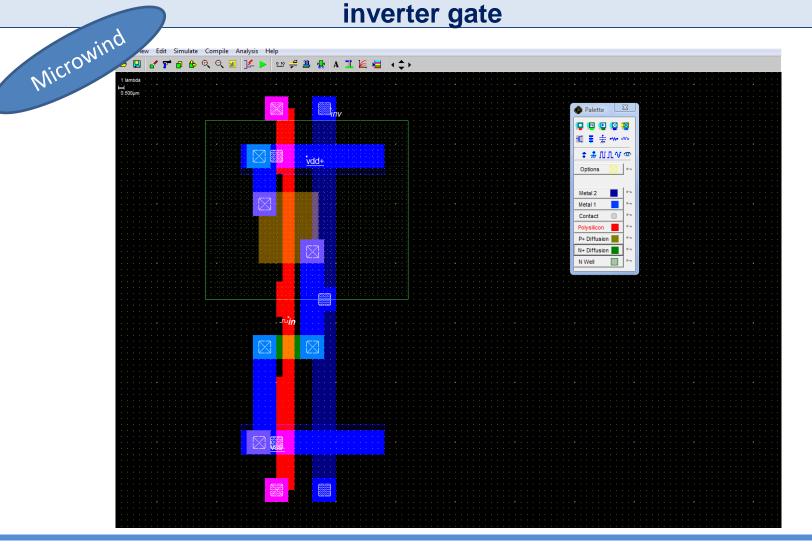

- Layout for an inverter

- Design rules

- Examples

- Masks are used in order to select the areas in silicon where the different fabrication steps must be applied.

- The graphical representation of required masks that define a circuit to be fabricated is named *layout*.

- A layout consists of a set of rectangles that represent the different layer masks:

- Substrates and wells

- Diffusion areas

- Polysilicon

- Metal interconnections

- Contacts and via

# N-well implantation

## P-well implantation

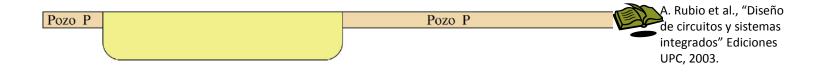

Active areas mask and thick oxide aimed at isolating transistors

Polysilicon for transistor gates

## N+ dopants implatation

## P+ dopants implantation

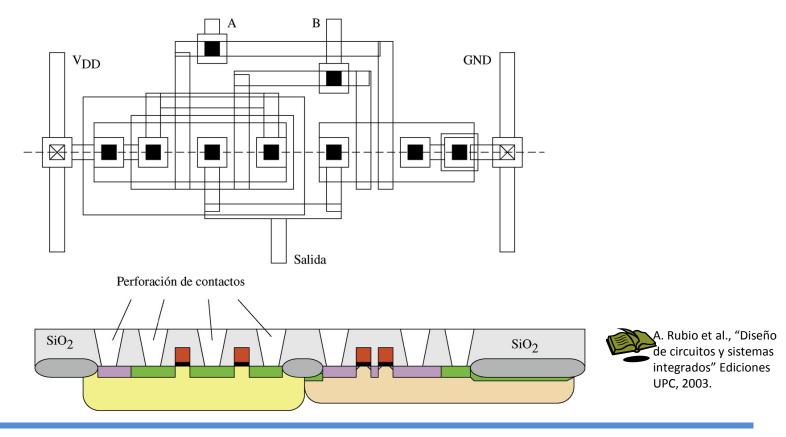

Adding insulator just keeping free the necessary areas to implement connections

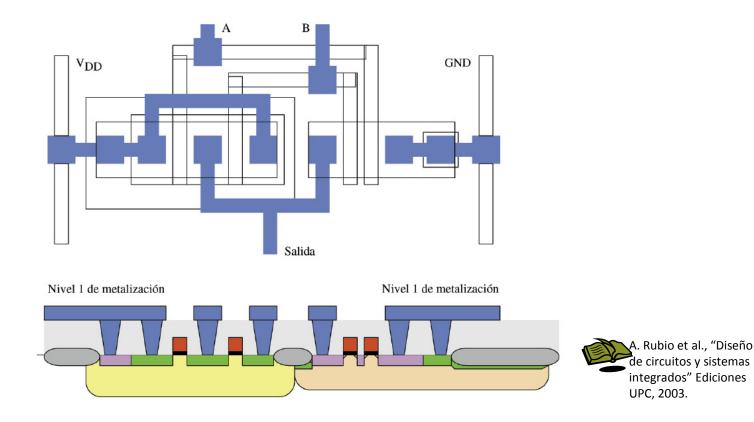

# Metalization: first layer

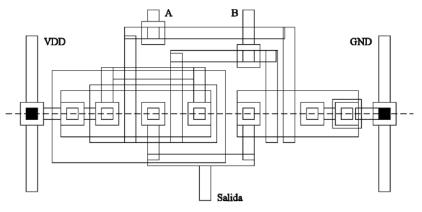

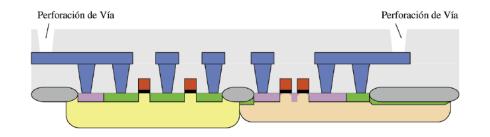

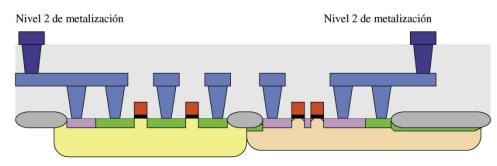

Adding insulator just keeping free the necessary areas to implement connections between two metal layers (via)

# Metalization: second layer

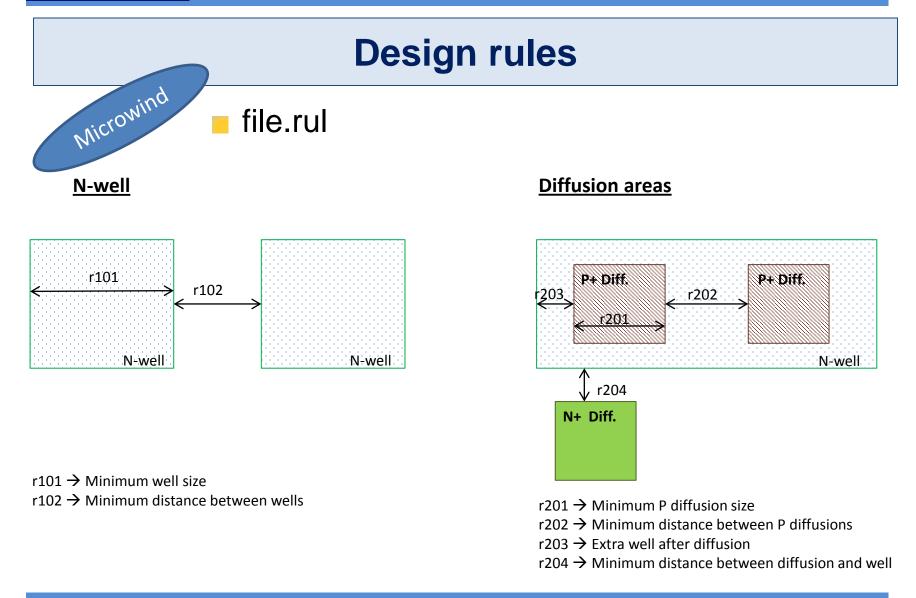

## **Design rules**

- They are the necessary set of rules that allows the designer to specify the design for its implementation on the silicon wafer.

- A complete set of design rules consists of the following elements:

- Set of layers

- Relations between the rectangles in the same layer

- Relations between the rectangles in different layers

- They fix geometric restrictions

## **Design rules**

- There are two types:

- Scalable.- They are represented in base to a parameter (λ)

- Adimensional rules.

- 2λ is the minimum size. It depends on the minimum dimension that is possible to etch in the silicion by means of the litographic process.

- During this course, scalable design rules are used. (Microwind CAD tool)

- In case of technologies beyond 0.18µm (lower dimensions), the scalability is not linear.

- These design rules imply the worst case => overdimensioned circuits

- Non scalable

- They are used by the industry

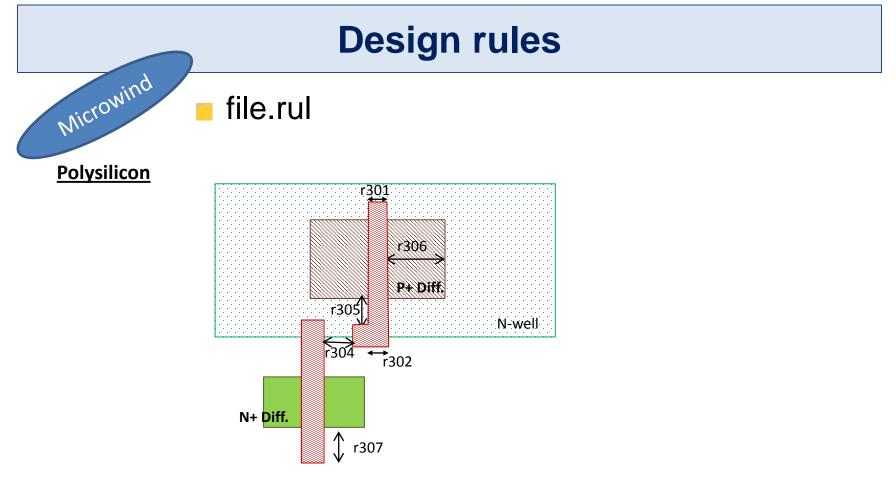

- r301  $\rightarrow$  Minimum polysilicon width

- r302  $\rightarrow$  Minimum polysilicon gate on diffusion N+

- r304  $\rightarrow$  Minimum distance between two polysilicon

r305  $\rightarrow$  Minimum distance between polysilicon and other diffusion

- r306  $\rightarrow$  Diffusion after polysilicon

- r307  $\rightarrow$  Extension of polysilicon after diffusion

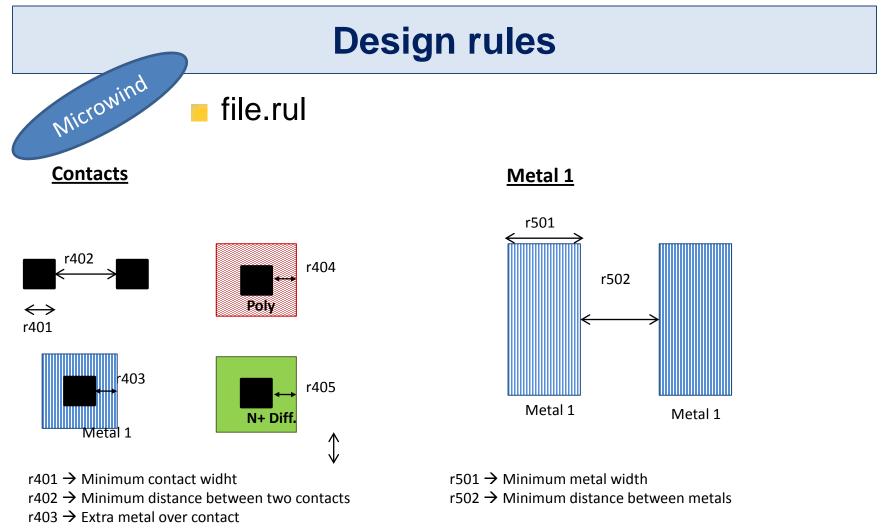

- r404  $\rightarrow$  Extra polysilicon over contact

- r405 ightarrow Extra diffusion over contact

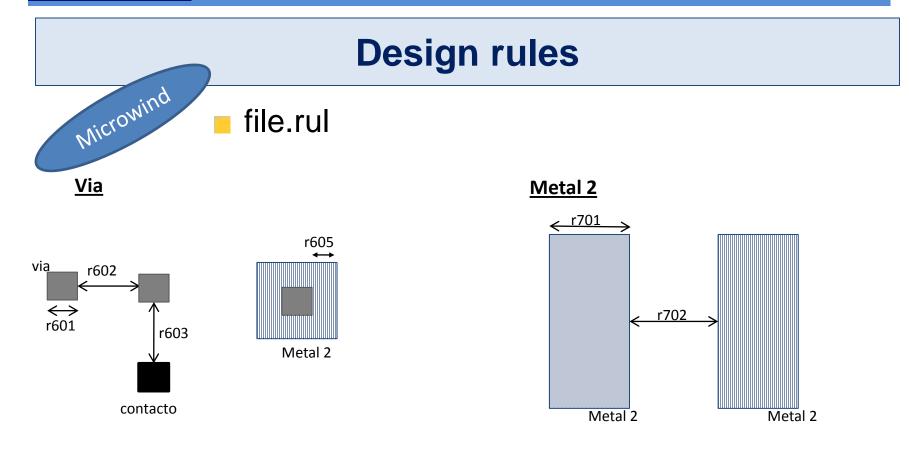

- r601  $\rightarrow$  Minimum via width

- r602  $\rightarrow$  Minimum distance between two via

- r603  $\rightarrow$  Minimum distance between via and contact

- r604  $\rightarrow$  Extra metal 1 over via

- r605  $\rightarrow$  Extra metal 2 over via

r701 → Minimum metal 2 width r702 → Minimum distance between two metal 2

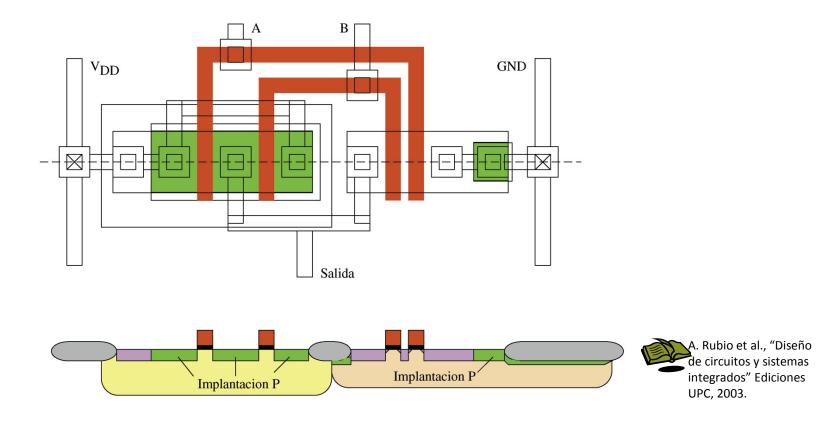

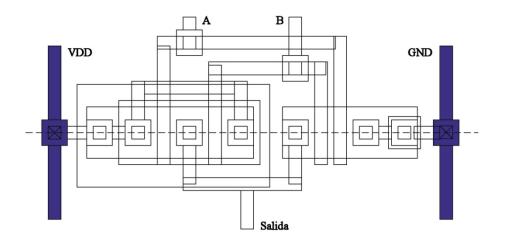

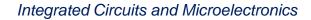

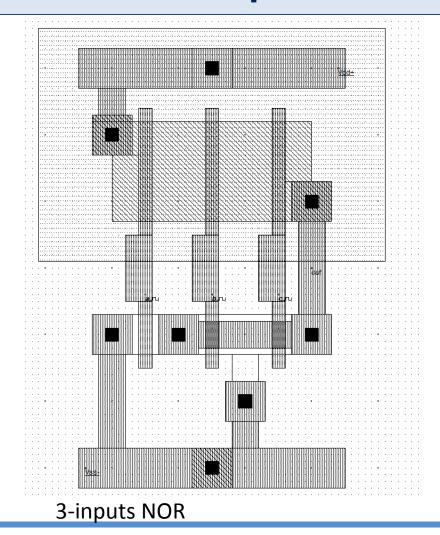

## **Examples**

## **Examples**

## **Examples**