# Unit 4. Single-ended and differential amplifiers

#### System-on-Chip and efficient electronic circuit integration techniques

Carlos III University of Madrid, Spain Electronics Technology Department

- **1. Single-ended amplifiers**

- 2. Miller effect

- **3. Cascode amplifiers**

- 4. Examples of single-ended amplifiers

- **5. Differential amplifiers**

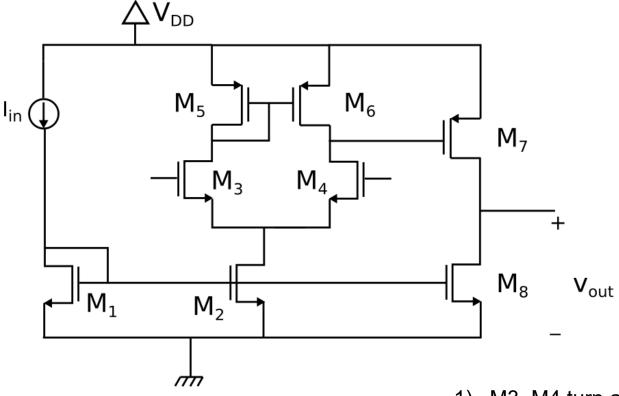

Basic structure of an operational amplifier

1) M3, M4 turn a voltage into a current.

Universidad

**Carlos III** de Madrid

uc3m

CC

- 2) M5, M6 turn a current into a voltage.

- 3) M7 turns a voltage into a current.

- 4) M8 turns a current into a voltage.

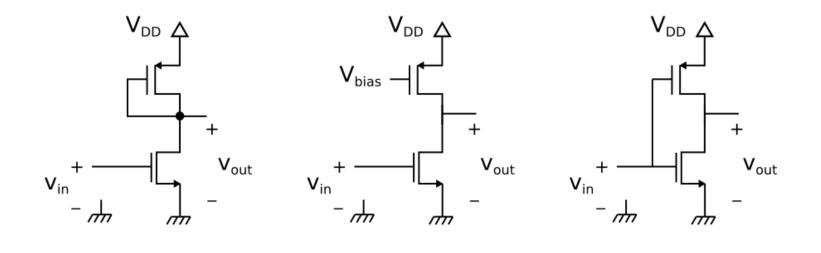

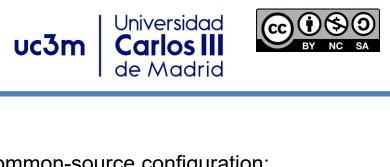

- Common-source configuration:

- High voltage, current and power gain.

- High input resistance.

- High output resistance.

- Inverting stage (180° phase shift between input and output).

- It is commonly used as the amplification stage in a multi-stage amplifier.

Universidad

**Carlos III** de Madrid

+

• Common-source configuration:

Universidad **Carlos III** de Madrid

uc3m

(cc)

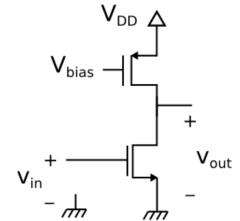

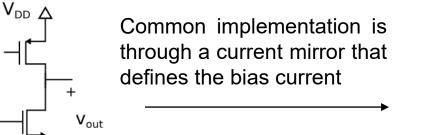

Active PMOS Load

Current-source Load

Push-Pull

• Common-source configuration:

V<sub>in</sub>

uc3m | Universidad Carlos III de Madrid

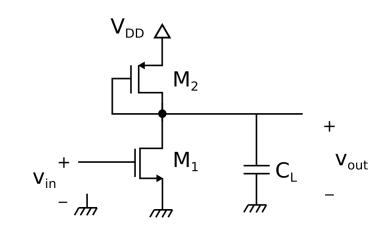

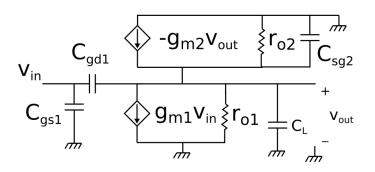

$$\frac{v_{out}}{v_{in}} \approx -\frac{g_{m1} - sC_{gd1}}{g_{m2} + s(C_{sg2} + C_{gd1} + C_L)}$$

$p_1 = -\frac{g_{m2}}{C_{sg2} + C_{gd1} + C_L} \qquad z_1 = \frac{g_{m1}}{C_{gd1}}$

#### **High resistance**

**Active PMOS Load**

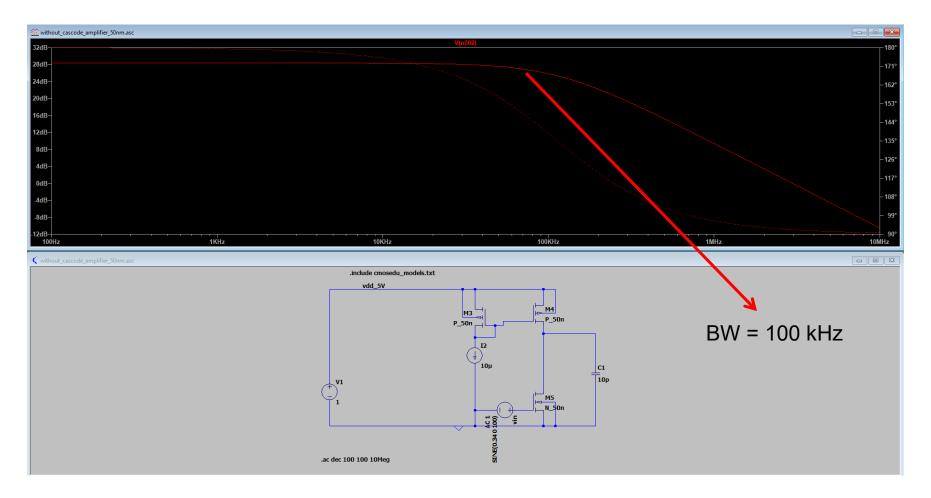

Common-source configuration: Frequency response

$p_{1} = -\frac{g_{m2}}{C_{sg2} + C_{gd1} + C_{L}} = -\frac{\sqrt{\frac{\mu_{p}C_{ox}W_{2}}{L_{2}}I_{D}}}{C_{sg2} + C_{gd1} + C_{L}} \qquad z_{1} = \frac{g_{m1}}{C_{gd1}}$

$p_1 < z_1 \rightarrow$  amplifier's bandwidth is limited by  $p_1$ .

To enhance amplifier's bandwidth:

Increase the bias current.

➢ Reduce L.

V<sub>in</sub>\_\_\_\_

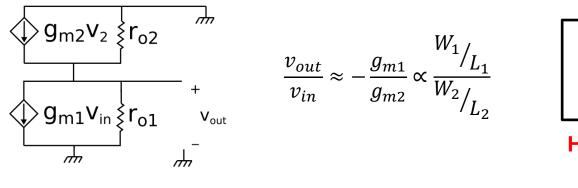

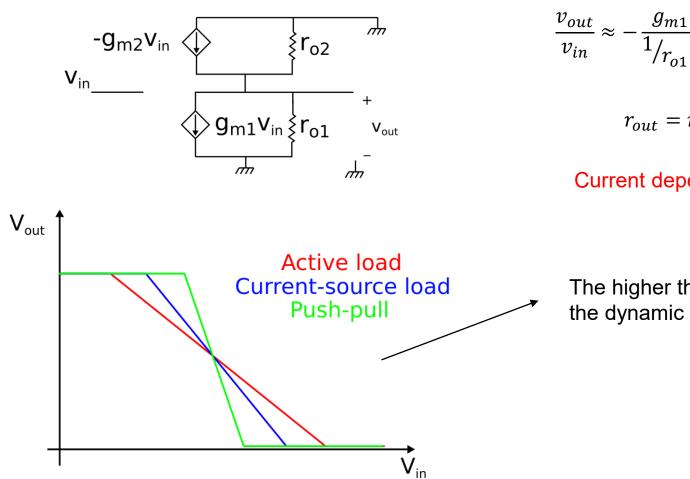

$$\frac{v_{out}}{v_{in}} \approx -\frac{g_{m1}}{1/r_{o1}} \propto \frac{1}{\sqrt{I_D}} \qquad r_{out} = r_{o1}||r_{o2}|$$

$$\frac{g_{m1}v_{in}}{r_{o1}} + v_{out} \qquad g_{m2} \text{ removed!}$$

$$p_1 \propto \frac{1}{L} \sqrt{\frac{I_D}{W}}$$

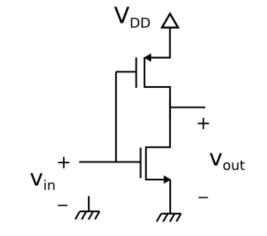

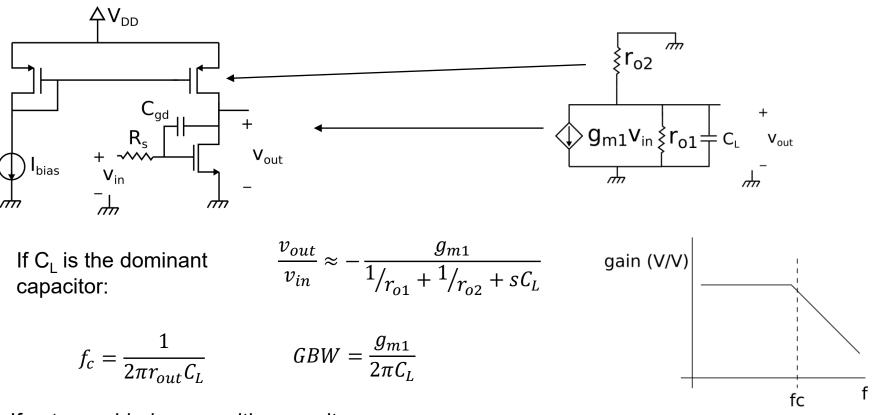

**Current-source Load**

Active PMOS Load

uc3m | Universidad Carlos III de Madrid

• Common-source configuration:

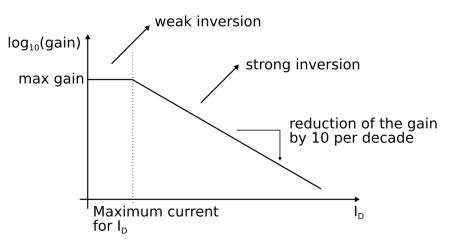

$$\frac{v_{out}}{v_{in}} \approx -\frac{g_{m1}}{1/r_{o1} + 1/r_{o2}} \propto \frac{1}{\sqrt{I_D}}$$

"Weak inversion"  $\rightarrow$  the gain is constant.

Frequency response:

$$p_1 \approx -\frac{1/r_{o1} + 1/r_{o2}}{C_{gd2} + C_{gd1} + C_L} \propto \frac{I_D}{WL}$$

V<sub>bias</sub> -

Vin

The higher the current the higher the bandwidth...but the lower the gain.

#### **Current-source Load**

Universidad

Carlos III de Madrid

Common-source configuration:

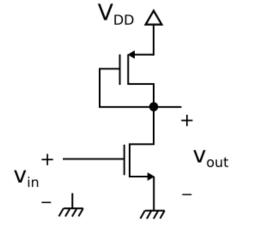

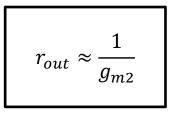

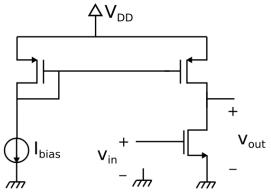

**Push-pull**

Universidad **Carlos III** de Madrid

uc3m

$$\frac{v_{out}}{v_{in}} \approx -\frac{g_{m1} + g_{m2}}{1/r_{o1} + 1/r_{o2}} \propto \frac{1}{\sqrt{I_D}}$$

$r_{out} = r_{o1} || r_{o2}$

Current depends on V<sub>DD</sub>.

The higher the gain the lower the dynamic range at the input

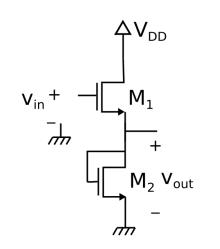

- Common-drain configuration:

- High current gain.

- High input resistance.

- Low output resistance.

- Low voltage gain.

- Non-inverting stage (no phase shift between input and output).

- It is commonly used as the output stage in a multi-stage amplifier to provide a low output resistance with a gain approximately equal to 1.

Universidad Carlos III de Madrid

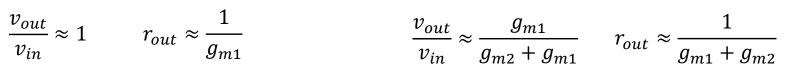

- Common-gate configuration:

- High voltage gain (similar to current source configuration).

- Current gain equal to 1.

- Low input resistance.

- High output resistance.

- Non-inverting stage (no phase shift between input and output).

- Input resistance can be increased with an external resistor.

Universidad

**Carlos III** de Madrid

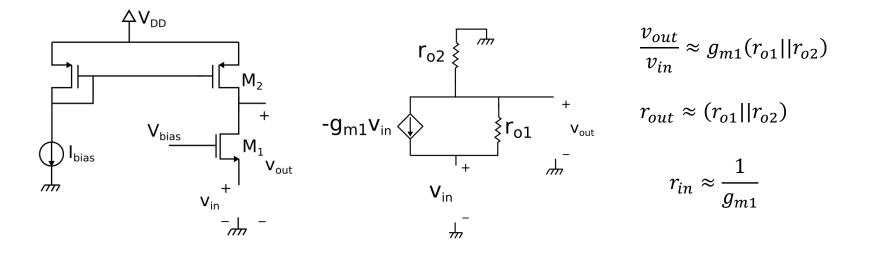

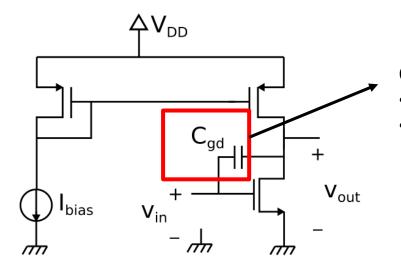

#### **2. Miller effect**

- $C_{gd}$  is multiplied by amplifier's gain:

- $\rightarrow$  Higher input capacitance  $\rightarrow$  slower circuit.

- Amplifier's bandwidth is decreased.

### 2. Miller effect

If not, considering parasitic capacitances:

$$\frac{v_{out}}{v_{in}} \approx -\frac{g_{m1}(r_{o1}||r_{o2})}{1 + s\left(R_s\left(C_{gs1} + C_{gd1}(1 + g_{m1}(r_{o1}||r_{o2}))\right) + (r_{o1}||r_{o2})(C_{gd1} + C_L)\right)}{\sqrt{1 + s\left(R_s\left(C_{gs1} + C_{gd1}(1 + g_{m1}(r_{o1}||r_{o2}))\right) + (r_{o1}||r_{o2})(C_{gd1} + C_L)\right)}}$$

$C_{ad1}$  is small but has a strong influence!

Previous dominant pole

Universidad **Carlos III** de Madrid

In high-frequency designs where we limit  $C_L$ :

- Miller effect dominates  $\rightarrow$  Reduce C<sub>GD</sub>.

- Small devices.

- Increase  $V_{GS} \rightarrow$  to increase the current.

In low-power designs (less current  $\rightarrow$  lower BW):

- C<sub>L</sub> dominates.

- Large devices.

- Reduce  $V_{GS} \rightarrow$  to reduce the current.

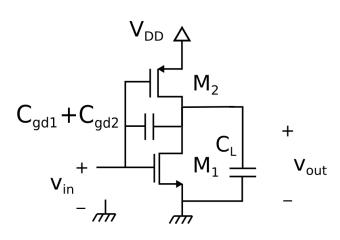

- Miller effect in push-pull configuration:

If  $C_L$  dominates and  $g_{m1}=g_{m2}$

$$\frac{v_{out}}{v_{in}} \approx -\frac{2g_{m1}}{1/r_{o1} + 1/r_{o2} + sC_L}$$

$f_c = \frac{1}{2\pi r_{out}C_L}$

**GBW** doubles

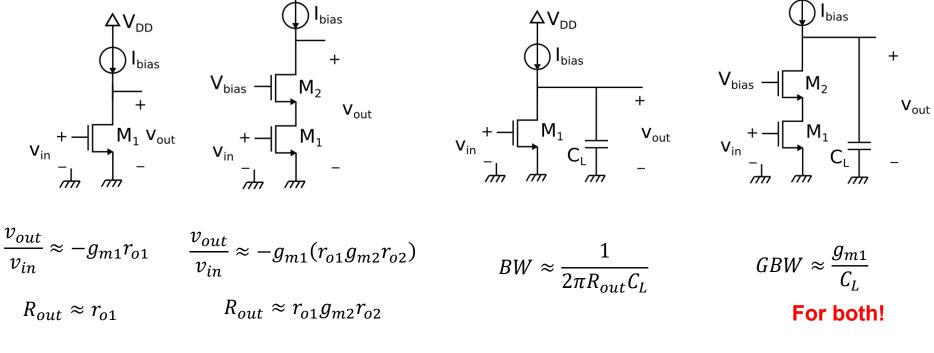

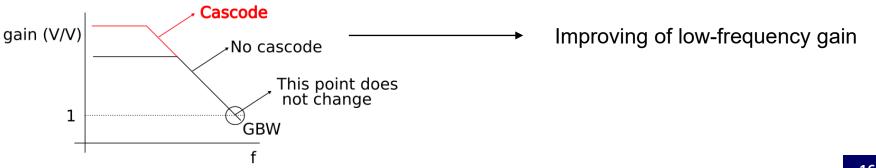

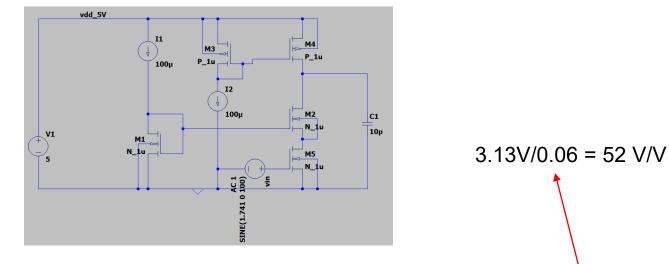

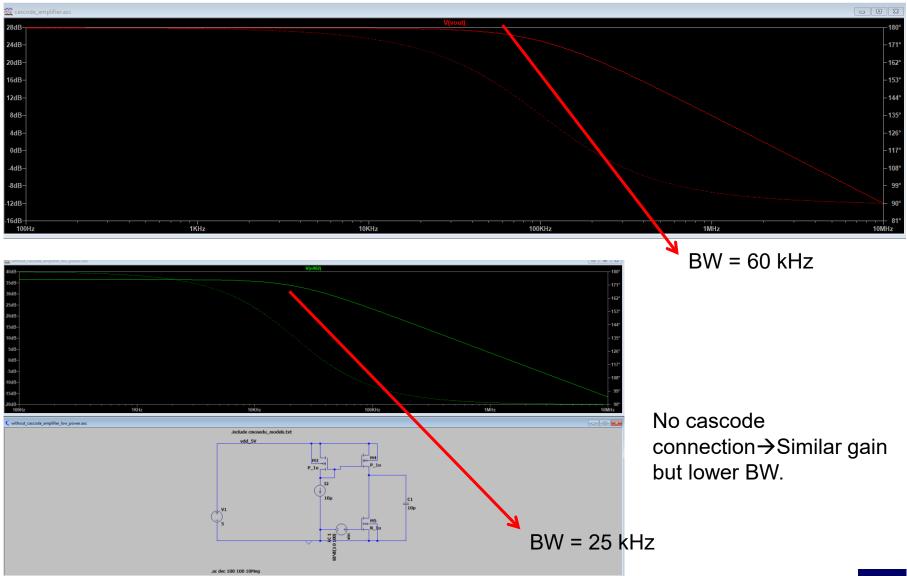

#### **3. Cascode amplifiers**

Advantages of cascode structures in comparison to previous architectures:

- **Higher output impedance**  $\rightarrow$  higher gain.

- For similar BW  $\rightarrow$  higher gain. For the same gain  $\rightarrow$  higher BW.

- Alleviate Miller effect  $\rightarrow$  suitable for high-frequency designs.

- Alleviate short-channel effects.

#### **3. Cascode amplifiers**

$\Delta V_{DD}$

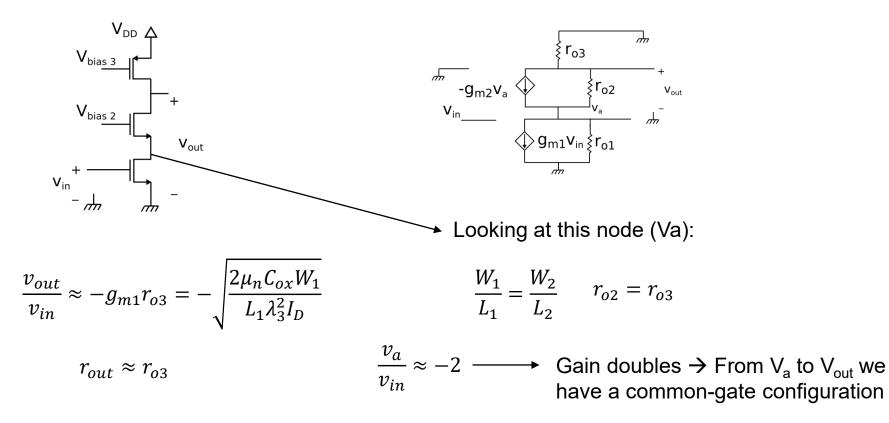

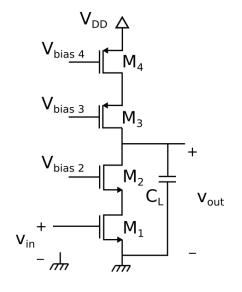

### **3. Cascode amplifiers**

To increase even more the output resistance and then the gain:

$$r_{out} \approx g_{m2} r_{o1} r_{o2} || g_{m3} r_{o3} r_{o4}$$

$$\frac{v_{out}}{v_{in}} \approx -g_{m1}r_{out}$$

uc3m

Universidad Carlos III de Madrid

$$f_c = \frac{1}{2\pi r_{out} C_L}$$

$$GBW = \frac{g_{m1}}{2\pi C_L}$$

- Telescopic cascode.

- Suitable for high voltage supply.

- L > 120 nm.

- Low input and output dynamic range.

$$V_{DD} \land r_{out} \approx g$$

$$r_{out} \approx g$$

$$M_1 \qquad M_2 \qquad V_{GG2} \qquad +$$

$$V_{in} \qquad M_1 \qquad M_2 \qquad C_L \qquad V_{out}$$

$$r_{out} \approx g_{m2} r_{o1} r_{o2}$$

$$\frac{v_{out}}{v_{in}} \approx -g_{m1}g_{m2}r_{o1}r_{o2}$$

$$f_c = \frac{1}{2\pi r_{out} C_L}$$

$$GBW = \frac{g_{m1}}{2\pi C_L}$$

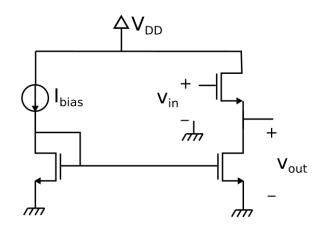

- Folded cascode.

- Suitable for low voltage supply.

- Enhanced input and output dynamic range.

- Power consumption doubles.

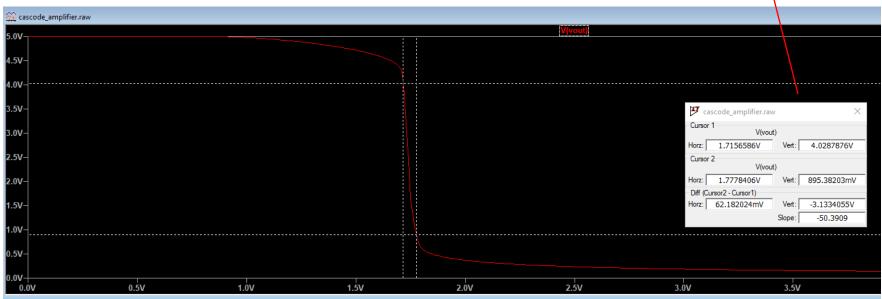

## 4. Examples of single-ended amplifiers

uc3m Universidad Carlos III de Madrid

CC

L = 1µm

## 4. Examples of single-ended amplifiers

uc3m | Universidad Carlos III de Madrid

CC

## 4. Examples of single-ended amplifiers

uc3m Carlos III de Madrid

Universidad

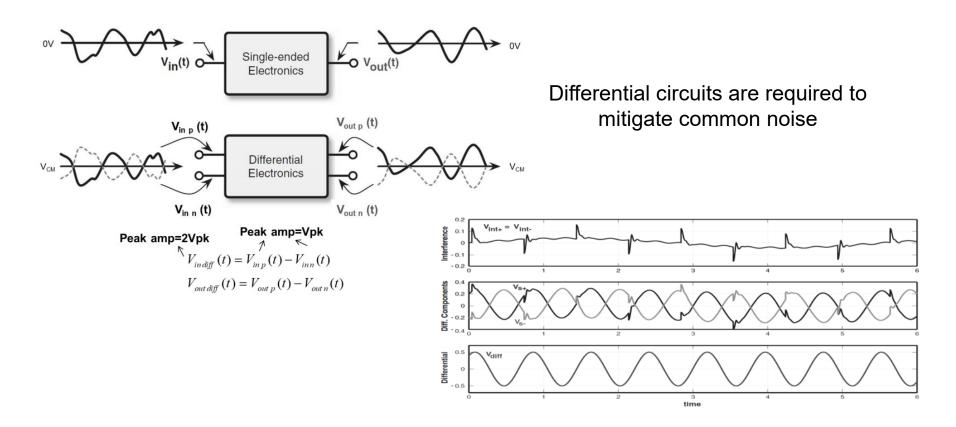

- Remove common signals between both channels (common interferences and even harmonics).

- In data converters  $\rightarrow$  +3 dB SNR improvement.

- Common-Mode Feed-Back (CMFB) control circuits are required.

- They consume more than "single-ended" circuits, but show better noise performance.

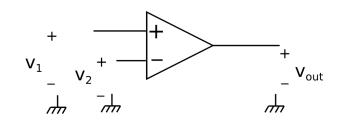

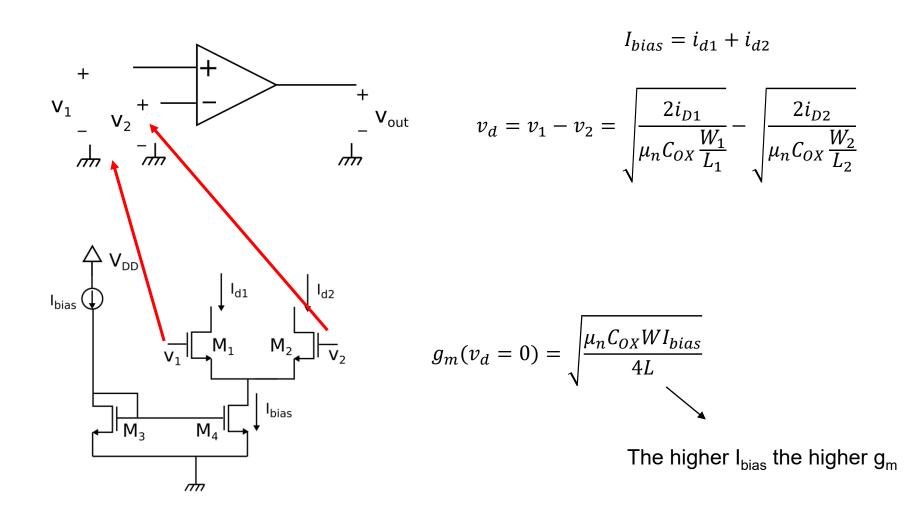

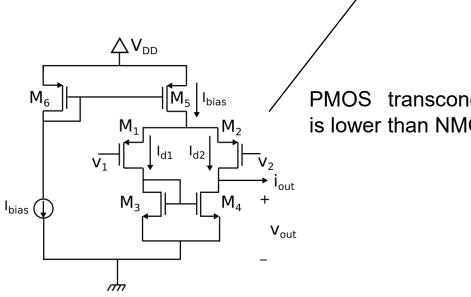

$V_1$ ,  $V_2$  y  $V_{out}$  are single-ended signals → they are referred to GND

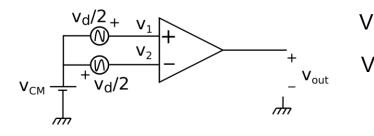

$$V_1 = V_{CM} + V_d/2$$

$V_2 = V_{CM} - V_d/2$

$$V_{d} = V_{1} - V_{2}$$

$V_{CM} = (V_{1} + V_{2})/2$

uc3m

$V_d$  is the differential mode input voltage  $V_{CM}$  is the common mode input voltage

1 11 \

Universidad

Carlos III de Madrid

V<sub>out</sub> can be expressed as a combination of both the differential and the common mode signals:

$$v_{out} = A_d v_d + A_{CM} v_{CM} = A_d (v_1 - v_2) + A_{CM} \left(\frac{v_1 + v_2}{2}\right)$$

Differential-mode gain Common-mode gain

$$CMRR = 20 \log_{10} \frac{A_d}{A_{CM}}$$

**Common-Mode Rejection Ratio**

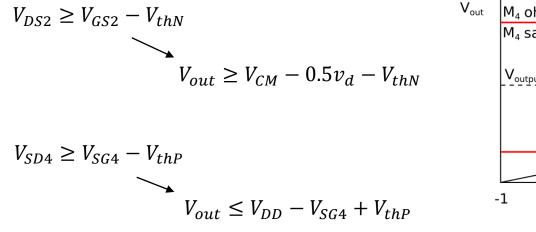

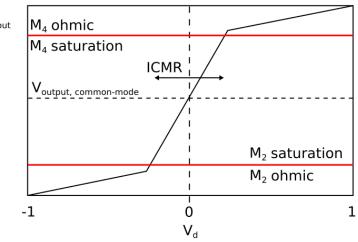

**ICMR (Input common-mode range):** V<sub>CM</sub> range to keep differential gain

$$i_{out} = i_{d1} - i_{d2}$$

uc3m

Universidad

Carlos III de Madrid

Si V<sub>d</sub>>0  $\rightarrow$  i<sub>out</sub> increases, V<sub>out</sub> increases Si V<sub>d</sub> <0  $\rightarrow$  i<sub>out</sub> decreases, V<sub>out</sub> decreases

$$g_{md}(v_d = 0) = \frac{\partial i_{out}}{\partial v_d} = \sqrt{\frac{\mu_n C_{OX} W I_{bias}}{L}} = g_{m1}$$

- Simple way of turning a differential signal into a single-ended one (Vout).

- Typically used in the input stage of operational amplifiers and comparators.

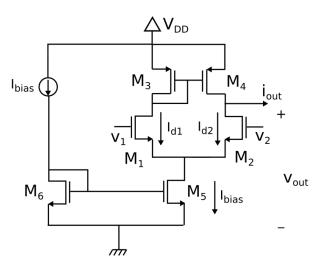

- Saturation requirements:

ΔV<sub>DD</sub>

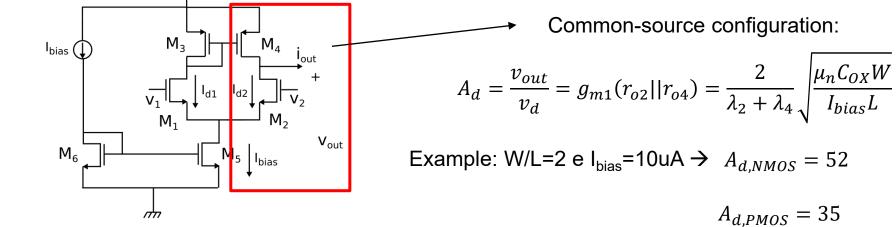

Equivalence with PMOS devices:

PMOS transconductance is lower than NMOS one

26

Universidad **Carlos III** de Madrid

uc3m

CC

• Differential amplifier with current-source load

CMFB  $\rightarrow$  to control output DC voltage

Universidad

Carlos III de Madrid

#### 28

### 5. Differential amplifiers

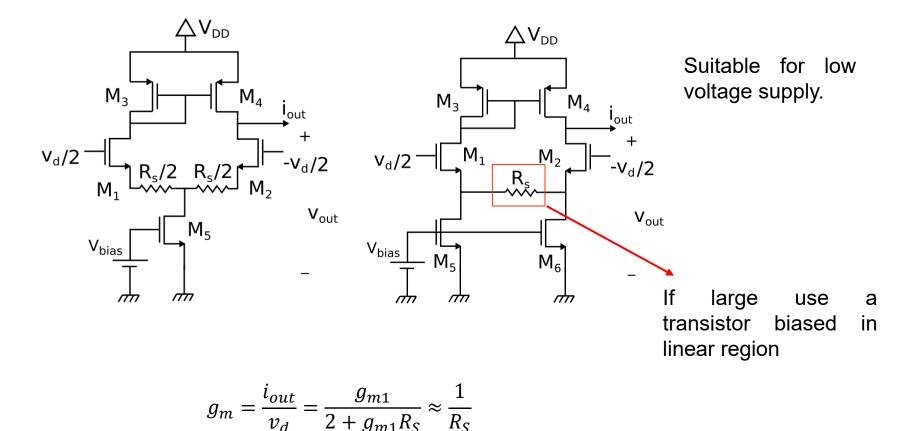

• Degenerated differential pair  $\rightarrow$  to improve linearity

Universidad **Carlos III** de Madrid

uc3m

CC

#### **Bibliography**

- Allen, P. E., & Holberg, D. R. (2002). CMOS analog circuit design. New York: Oxford University Press.

- R. Jacob Baker. 2010. CMOS Circuit Design, Layout, and Simulation (3rd. ed.). Wiley-IEEE Press.

Simulations are performed through software LTSPice, provided courtesy of <u>Analog Devices</u> and authored by <u>Mike Engelhardt</u>.

Spice models of transistors come from <u>http://cmosedu.com/</u>, website maintained by <u>R. Jacob</u> <u>Baker</u>.