## **Unit 6. Comparators**

### System-on-Chip and efficient electronic circuit integration techniques

Carlos III University of Madrid, Spain Electronics Technology Department

- **1. Basic concepts**

- **2. Open-loop comparators**

- **3. Hysteresis**

- 4. Regenerative or latched comparators

# **1. Basic concepts**

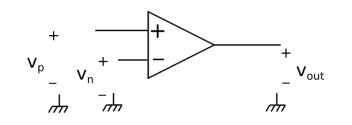

• A comparator is defined as a circuit with a binary output  $V_{out}$  whose value depends on the comparison between two inputs  $V_p$  and  $V_n$ .

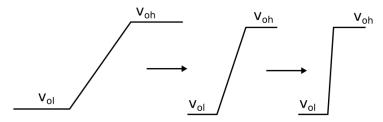

$$v_{out} = -\begin{cases} v_{oh} \operatorname{si} v_{p} > v_{n} \\ v_{ol} \operatorname{si} v_{p} < v_{n} \end{cases}$$

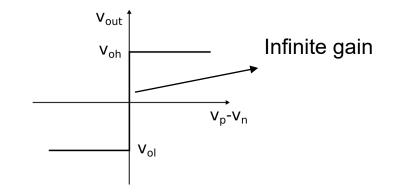

$$v_{out} = -\begin{cases} v_{oh} \operatorname{si} v_{p} - v_{n} > v_{ih} \\ A_{V}(v_{p} - v_{n}) \operatorname{si} v_{il} < v_{p} - v_{n} < v_{ih} \\ v_{ol} \operatorname{si} v_{p} - v_{n} < v_{il} \end{cases}$$

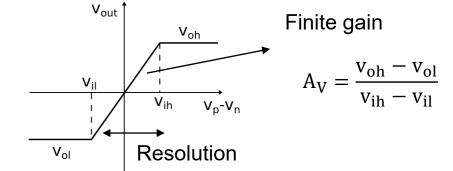

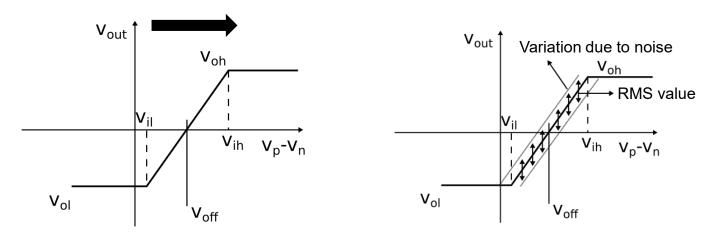

- The curve is usually not centered at zero  $\rightarrow$  input offset (V<sub>off</sub>)  $\rightarrow$  highly dependent parameter.

- ICMR: range of DC input voltage to have the devices working in saturation → similar to amplifiers.

- Noise in comparators is of special relevance due to random variations in the gain → jitter issues and resolution losses in data converters.

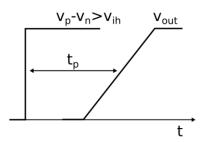

- Propagation delay (tp) is limited by two phenomena:

- 1) Frequency response.

- 2) SR: the highest current available.

#### 1) Frequency response:

Assuming a first-order filter with dominant pole  $\rightarrow t_p = \frac{1}{2\pi f_p} ln \frac{2k}{2k-1}$

$$\mathbf{k} = \frac{\mathbf{v}_{\mathrm{p}} - \mathbf{v}_{\mathrm{n}}}{\left(\mathbf{v}_{\mathrm{p}} - \mathbf{v}_{\mathrm{n}}\right)_{\mathrm{min}}}$$

**2) SR:**  $t_p = \frac{v_{oh} - v_{ol}}{2SR}$

The propagation delay varies with the input signal  $V_p-V_n \rightarrow$

The highest the  $V_p$ - $V_n$  the lowest the propagation delay with a minimum one defined by SR.

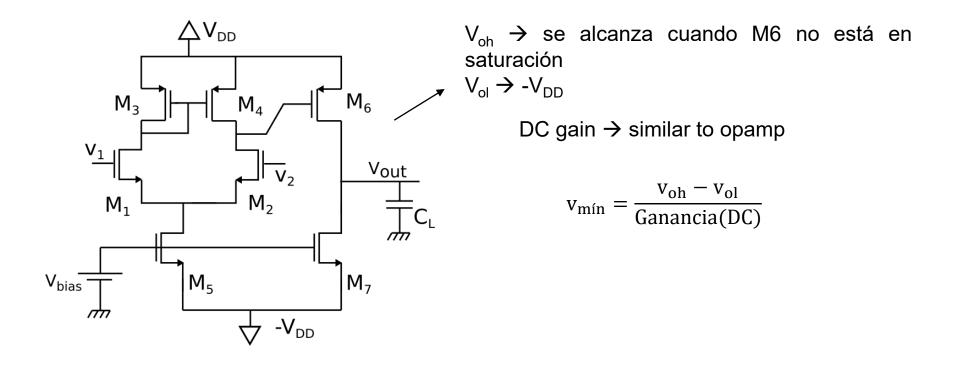

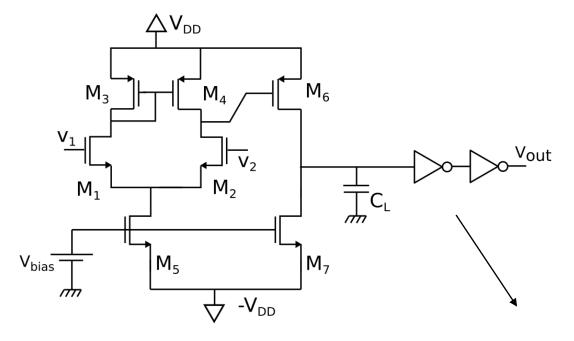

What do we need for a comparator? → A differential input stage and enough gain → for instance, Miller opamp accomplishes with these requirements.

Universidad

Carlos III de Madrid

uc3m

• Amplifiers **with no compensation circuitry** to avoid limiting bandwidth and enable a faster response.

• To improve resolution, we can use digital buffers at the output:

- High ICRM

- High power consumption

Universidad

Carlos III de Madrid

High offset and propagation delay

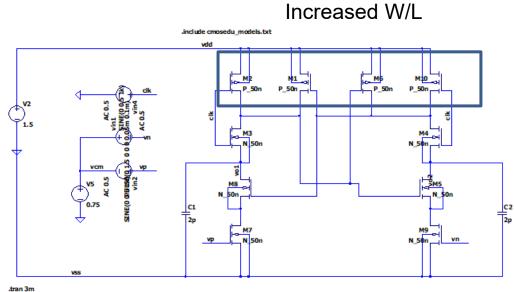

Aspect ratio increases: with a factor of  $2.72 \rightarrow$  best solution in delay Higher aspect ratio  $\rightarrow$  to reduce the number of stages

uc3m

This way we can feed high  $C_L$

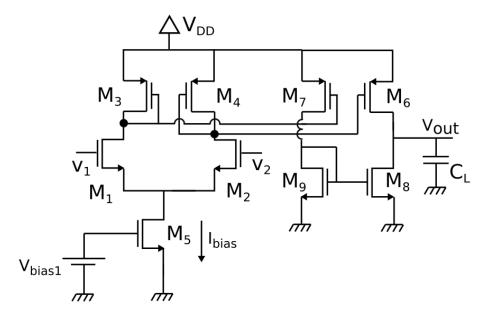

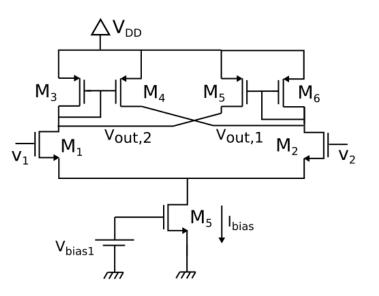

• Push-pull architecture:

- High current in C<sub>L</sub>.

- High output resistance → slow comparator due to a pole in the second stage.

• Self-supply architecture:

- High current in C<sub>L</sub>, with lower power consumption.

- Asymmetry, lower propagation delay from the negative input (V<sub>2</sub>).

Universidad **Carlos III** de Madrid

uc3m

CC

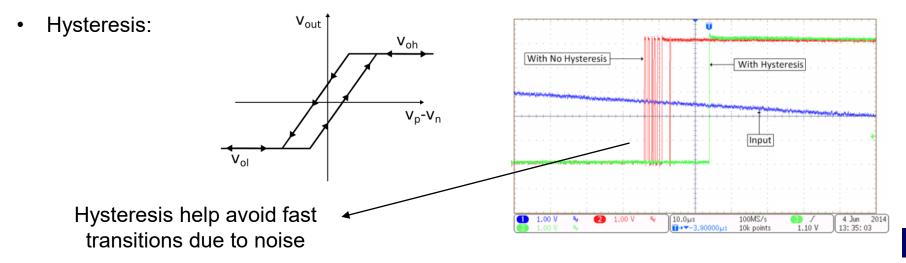

# **3. Hysteresis**

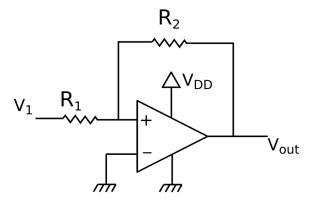

• External hysteresis: with positive feedback.

• Internal hysteresis: with positive feedback.

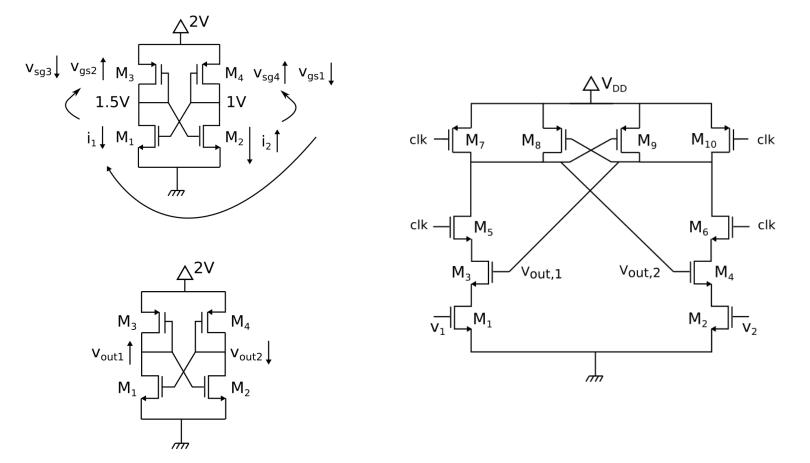

# 4. Regenerative or latched comparators

- They make use of a positive feedback.

- Two phases consecutive in time: firstly, the value of the inputs is stored and the comparison between them is started, and secondly, the comparison is finished.

Universidad

**Carlos III** de Madrid

uc3m

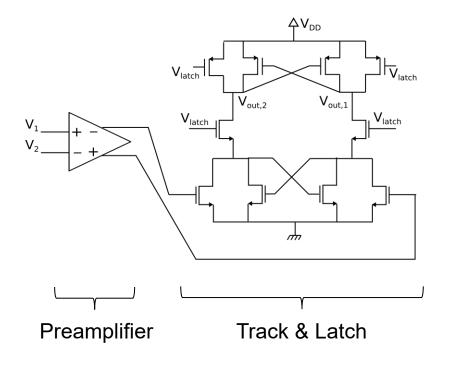

• To distinguish between both phases a clock signal is used.

# 4. Regenerative or latched comparators

uc3m | Universidad Carlos III de Madrid

(cc)

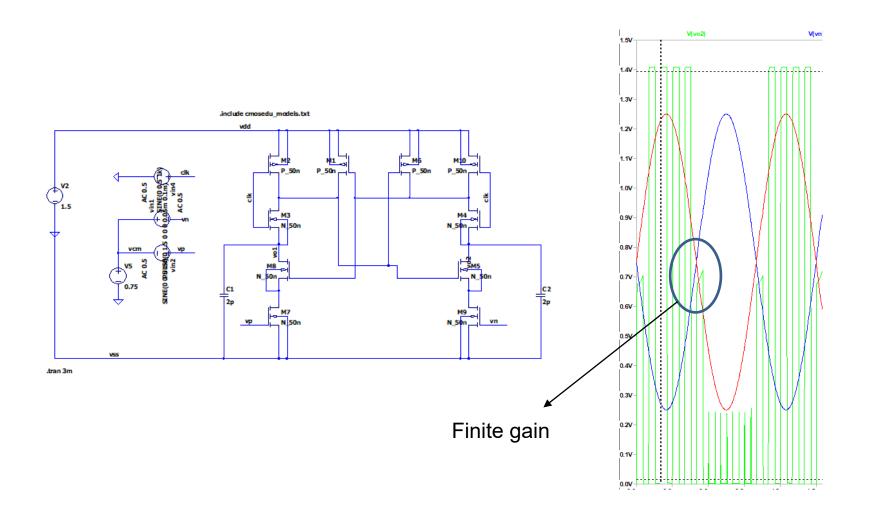

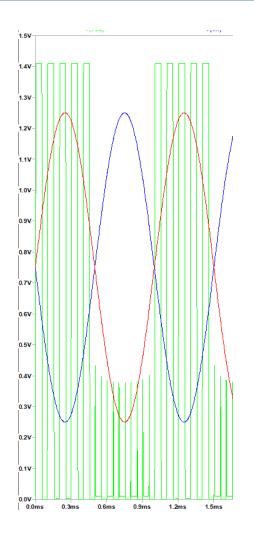

• Example in 50-nm:

### 4. Regenerative or latched comparators

Example in 50-nm: •

Universidad Carlos III de Madrid

uc3m

# 4. Regenerative or latched comparators

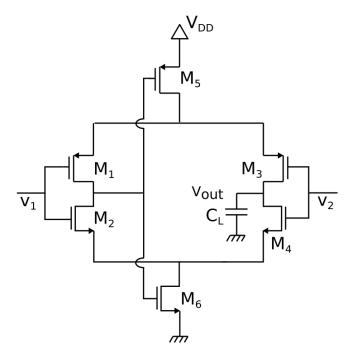

It is the most common structure nowadays. The preamplifier is just a differential pair or a buffer with small gain (10 or so) A switched capacitor input can still be used to mitigate offset and 1/f noise.

Simple preamplifier to mitigate kickback and reduce requirements of latch stage. The latch stage alternates between a reset phase and a positive feedback phase that quickly generates saturated digital signals.

### **Bibliography**

- Allen, P. E., & Holberg, D. R. (2002). CMOS analog circuit design. New York: Oxford University Press.

- R. Jacob Baker. 2010. CMOS Circuit Design, Layout, and Simulation (3rd. ed.). Wiley-IEEE Press.

Simulations are performed through software LTSPice, provided courtesy of <u>Analog Devices</u> and authored by <u>Mike Engelhardt</u>.

Spice models of transistors come from <u>http://cmosedu.com/</u>, website maintained by <u>R. Jacob</u> <u>Baker</u>.