### Diseño de sistemas electrónicos

Universidad Carlos III de Madrid

Dpto. Tecnología Electrónica

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

## Índice

- Conceptos principales

- I<sup>2</sup>C: Comunicación serie síncrona a 2 hilos

- SPI: Comunicación serie síncrona a 3/4 hilos

## **Conceptos Principales**

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

## Comunicación serie y paralelo

- En una comunicación serie, la información se divide en trozos (normalmente palabras o bytes) y cada trozo se transmite bit a bit a través de la línea

- En una comunicación paralelo, la información también se divide en trozos (normalmente palabras o bytes), pero ahora cada trozo se transmite al mismo tiempo a través de varias líneas. Es casi lo mismo que la comunicación por bus, pero en este caso no es necesario que más de un dispositivo esté conectado

Figura 1: https://www.bb-elec.com/Learning-Center/All-White-Papers/Serial/Parallel-Communication-Overview.aspx Figura 2: https://www.bb-elec.com/Learning-Center/All-White-Papers/Serial/Parallel-Communication-Overview.aspx

http://dte.uc3m.es

Figura 2

BY NC SA

1. Conceptos principales

Comunicación

serie síncrona

Tema 6:

2. I<sup>2</sup>C

3. SPI

- En la comunicación serie, los dispositivos pueden ser conectados en cada punto del cable, mientras que en la comunicación paralelo los cables van directamente de un dispositivo a otro, sin más dispositivos entre medias. Por lo tanto, podemos conectar muchos dispositivos entre sí de forma externa a la CPU

- La comunicación serie sólo utiliza uno/dos cables, mientras que la comunicación en paralelo utiliza varios cables. Por lo tanto, es mejor en una de sus opciones para la comunicación con grandes distancias, hablando de montaje y gestión de la instalación (utilizando métodos para no perder señal con la distancia) y hay menos problemas de interferencias entre los propios cables

- Así que tenemos una solución técnica peor que la comunicación paralela (teóricamente más lenta), pero mejor en la práctica (montaje e instalación)

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

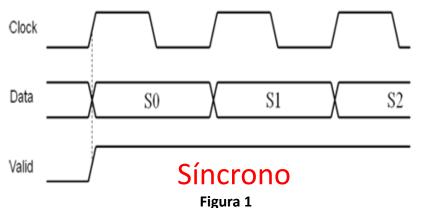

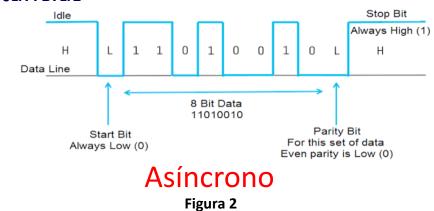

## Protocolo síncrono y asíncrono

- En la comunicación en serie es necesario buscar métodos y puntos de sincronismo para indicar la existencia de cada bit, para indicar el punto de inicio de cada palabra, el punto final de cada palabra, etc. De acuerdo con el sincronismo de bits, hay:

- <u>Protocolo síncrono</u>: Cuando hay una señal de reloj explícita que indica la validez del bit transmitido -> Para comunicaciones internas dentro de la CPU debido al rendimiento

- <u>Protocolo asíncrono</u>: Cuando la señal de reloj no existe, por lo tanto la sincronización del emisor y el receptor debe hacerse de otra manera -> Para las comunicaciones externas debido a las distancias

Figura 2: https://electricalfundablog.com/asynchronous-transmission-communication-characteristics-process-of-data-flow-advantages-and-disadvantages/

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

## Comunicación serie síncrona (I)

- Es la comunicación serie en la que la secuencia de los diferentes bits es controlada por una **señal de reloj** explícita, que valida el bit en la línea por "*nivel*" o por "*flanco*"

- No es necesario que la señal del reloj sea periódica ni continua, pero normalmente se llama reloj (clk), aunque el nombre propio debería ser señal de validación

- Esta señal de reloj es muy crítica y no puede ser distorsionada. Por lo tanto, esta es la razón por la que la comunicación serie sincrónica se utiliza sólo dentro de la CPU para distancias muy cortas

- Esto significa que la comunicación serie sincrónica está generalmente diseñada para comunicaciones entre chips dentro de circuitos integrados y para ser implementada con "cables" cortos

- Las pistas son muy estrechas y cortas, por lo que su resistencia y capacidad son muy bajas, y por lo tanto la transición entre el "0" y el "1" es casi perfecta y las señales (incluyendo las señales del reloj) son perfectas

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

## Comunicación serie síncrona (II)

Ha habido muchos protocolos para implementar esta comunicación, pero la industria sólo ha seleccionado muy pocos de ellos estos últimos años (principalmente propuesta del fabricante):

- |2C

- SPI

- MICROWIRE

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

## I<sup>2</sup>C: Propiedades

- Fue especificado por Philips (Inter Integrated Circuits)

- Proporciona una interfaz a 2 hilos

- SDA: Línea de datos (bidireccional)

- **SCL**: Enable / Línea del reloj

- Se especifica en niveles TTL (es decir, 2 niveles de tensión, por ejemplo 0-5V o similar), por lo que es imposible modular la información utilizando diferentes tensiones o frecuencias

- No permite la comunicación full-duplex, pero permite semi-duplex

- La selección de los dispositivos se realiza mediante un sistema de direccionamiento y no por líneas hardware. La trama está limitada con una condición de START y una condición de STOP

- Velocidad: 100 Kbps / 400 Kbps / 1 Mbps / 3,4 Mbp

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

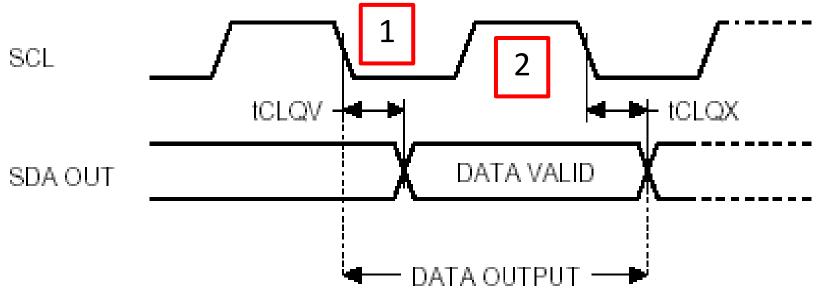

## I<sup>2</sup>C: Funcionamiento a nivel de bit

- Primera condición: Los datos no pueden ser modificados cuando la línea SCL tiene el valor de nivel "1". Éstos sólo pueden ser cambiados cuando aparece un flanco descendente en SCL

- Segunda condición: La validación del bit se hace por nivel alto ("1") en la línea SCL

http://dte.uc3m.es

Figura 1: Archivo "M24C16, M24C08, M24C04, M24C02, M24C01 - Product data sheet", 2004, Pag. 6

Figura 2: https://d3.xlrs.eu/conectividad/i2c/

Figura 1

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

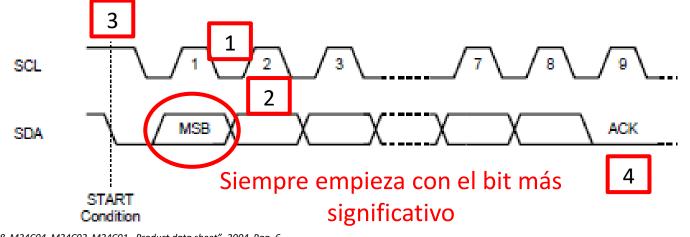

## I<sup>2</sup>C: Funcionamiento a nivel de carácter

- <u>Tercera condición</u>: La primera condición no es válida con un START o un STOP en la trama. Por ejemplo, se puede ver en la imagen de abajo el cronograma para el START en el envío de un carácter (SCL = "1" y SDA con flanco descendente)

- <u>Cuarta condición</u>: Proporciona reconocimiento de recepción (ACK) para cada carácter (excepto en el último byte en la operación de lectura)

- Abajo se puede ver el cronograma para el ACK en el envío de un carácter: Después de enviar 8 bits de datos, el emisor pone la línea SDA a "0" y el receptor reconoce el acuse

http://dte.uc3m.es

Figura 1: Archivo "M24C16, M24C08, M24C04, M24C02, M24C01 - Product data sheet", 2004, Pag. 6

Figura 2: https://d3.xlrs.eu/conectividad/i2c/

Figura 1

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

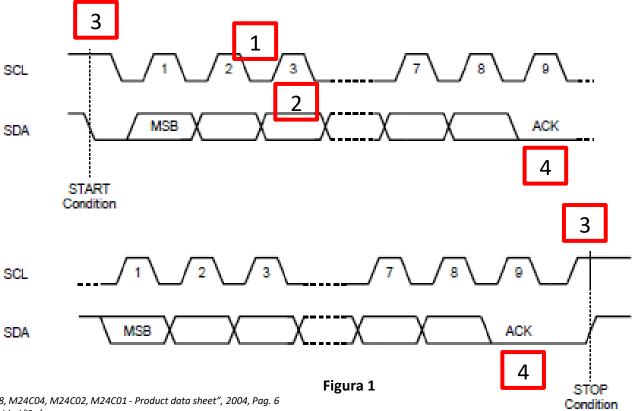

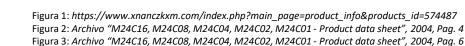

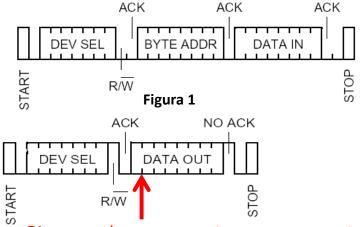

### I<sup>2</sup>C: Funcionamiento a nivel de trama

Ahora se puede ver en la imagen de abajo el cronograma de una trama completa entre START (SCL = "1" y SDA tiene un flanco descendente en el primer carácter) y STOP (SCL = "1" y SDA tiene un flanco ascendente en el último carácter)

Figura 1: Archivo "M24C16, M24C08, M24C04, M24C02, M24C01 - Product data sheet", 2004, Pag. 6

Figura 2: https://d3.xlrs.eu/conectividad/i2c/

1. Conceptos principales

2. I<sup>2</sup>C

3. SPI

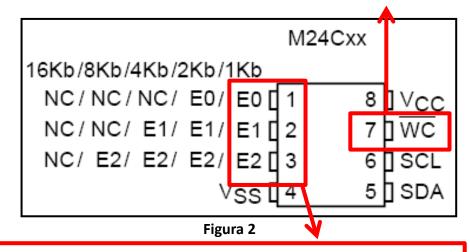

## I<sup>2</sup>C: Memoria M24Cxx

Figura 1

#### Write Control = 1 -> Memoria deshabilitada

#### Table 3. Device Select Code

|                    | Device Type Identifier <sup>1</sup> |    |    | Chip Enable <sup>2,3</sup> |     |    | R₩ |    |

|--------------------|-------------------------------------|----|----|----------------------------|-----|----|----|----|

| DEVSEL             | b7                                  | b6 | b5 | b4                         | b3  | b2 | b1 | b0 |

| M24C01 Select Code | 1                                   | 0  | 1  | 0                          | E2  | E1 | E0 | R₩ |

| M24C02 Select Code | 1                                   | 0  | 1  | 0                          | E2  | E1 | E0 | R₩ |

| M24C04 Select Code | 1                                   | 0  | 1  | 0                          | E2  | E1 | A8 | R₩ |

| M24C08 Select Code | 1                                   | 0  | 1  | 0                          | E2  | A9 | A8 | R₩ |

| M24C16 Select Code | 1                                   | 0  | 1  | 0                          | A10 | A9 | A8 | R₩ |

Figura 3

0: Micro -> Memoria

1: Memoria -> Micro

http://dte.uc3m.es

Figura 4: https://d3.xlrs.eu/conectividad/i2c/

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

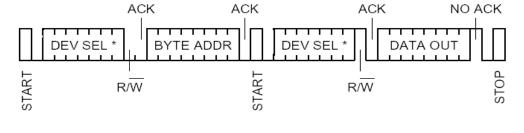

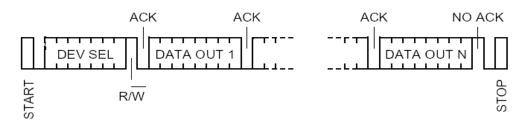

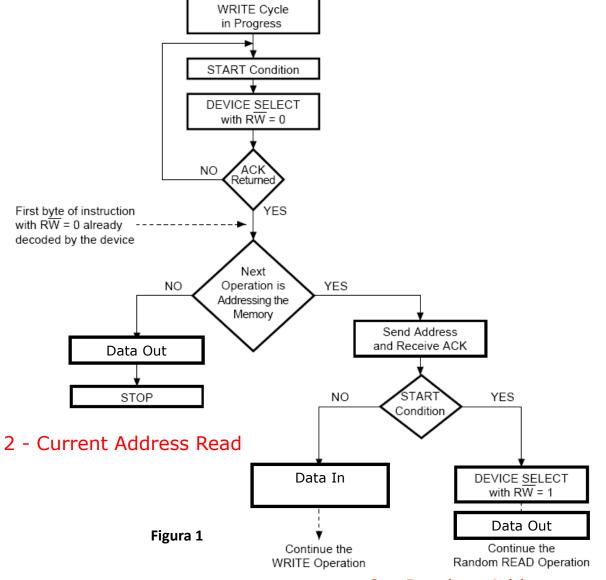

# I<sup>2</sup>C: Memoria M24Cxx - Operaciones

BYTE WRITE

1

CURRENT ADDRESS READ

2

RANDOM ADDRESS READ

3

SEQUENTIAL CURRENT READ

4

Siempre hay un puntero que apunta a la dirección actual

Figura 2

Figura 1: Archivo "M24C16, M24C08, M24C04, M24C02, M24C01 - Product data sheet", 2004, Pag. 9

Figura 2: Archivo "M24C16, M24C08, M24C04, M24C02, M24C01 - Product data sheet", 2004, Pag. 11

Figura 3: https://d3.xlrs.eu/conectividad/i2c/

http://dte.uc3m.es

Hay que

enviar la

instrucción

"Byte Write",

interrumpirla,

y luego enviar

la instrucción

"Current

Address

Read"

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

## I<sup>2</sup>C: Memory M24Cxx - Diagrama de flujo

Diagrama de flujo para las secuencias de lectura/escritura en el programa del microcontrolador

Figura 1: Archivo "M24C16, M24C08, M24C04, M24C02, M24C01 - Product data sheet", 2004, Paq. 10 Figura 2: https://d3.xlrs.eu/conectividad/i2c/

1 - Byte Write

3 - Random Address read

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

## I<sup>2</sup>C: Microcontrolador LPC2129

- Permite que la comunicación maestra y la comunicación esclava

- Los pines están conectados en forma de colector abierto:

- P0.2 SCL

- P0.3 SDA

- Los registros correspondientes para I2C son:

| Name     | Description                             | Access     | Reset Value* | Address    |

|----------|-----------------------------------------|------------|--------------|------------|

| I2CONSET | I <sup>2</sup> C Control Set Register   | Read/Set   | 0            | 0xE001C000 |

| I2STAT   | I <sup>2</sup> C Status Register        | Read Only  | 0xF8         | 0xE001C004 |

| I2DAT    | I <sup>2</sup> C Data Register          | Read/Write | 0            | 0xE001C008 |

| I2ADR    | I <sup>2</sup> C Slave Address Register | Read/Write | 0            | 0xE001C00C |

| I2SCLH   | SCL Duty Cycle Register High Half Word  | Read/Write | 0x04         | 0xE001C010 |

| I2SCLL   | SCL Duty Cycle Register Low Half Word   | Read/Write | 0x04         | 0xE001C014 |

| I2CONCLR | I <sup>2</sup> C Control Clear Register | Clear Only | NA           | 0xE001C018 |

Figura 1: https://hydolabz.com/development-boards-quick-start-boards-c-206\_67/lpc2129-arm-header-board-rhydolabz-p-412.html

Figura 2: Archivo "LPC2119/2129/2194/2292/2294 - User manual", 2004, Pag. 171

Figura 3: https://d3.xlrs.eu/conectividad/i2c/

Figura 1

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

# I<sup>2</sup>C: Microcontrolador LPC2129 - Operaciones

#### Envío de START:

- SI = 0

- STA = 1

- Cuando se produce el START, la línea SI se activa

- Finalmente hay que limpiar el flag de START

#### • Envío de un carácter:

- Se coloca el dato en el registro I2DAT

- SI = 0

- SI cambia a "1" cuando la transmisión ha terminado y el registro I2STAT informa si ha llegado el ACK

### • Recepción de un carácter:

- SI = 0

- Espera a que el registro I2STAT informe de que hay un nuevo carácter y la línea SI cambie a "1".

- Se lee el registro I2DAT (los datos están ahí)

#### • Envío de STOP:

- STO = 1

- SI = 0

http://dte.uc3m.es

gura: https://d3.xlrs.eu/conectividad/i2c/

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

## **SPI: Propiedades**

- Serial Peripheral Interface es una interfaz a 3/4 hilos (como I<sup>2</sup>C, pero con 2 líneas de datos):

- SCK: Reloj

- MOSI (o SI): Master out Slave in

- MISO (o SO): Master in Slave out

- <u>CS#</u>: Chip Select

- Se especifica en niveles TTL (es decir, 2 niveles de tensión, por ejemplo 0-5V o similar), por lo que es imposible modular la información utilizando diferentes tensiones o frecuencias

- La selección del dispositivo se realiza mediante un línea hardware (Chip Select - CS)

- Tiene 2 modos de funcionamiento, dependiendo de la fase y la polaridad de la línea SCK

- En el **modo 0**, SI pone los datos con un flanco ascendente y SO captura los datos con un flanco descendente

- En el **modo 1**, SI pone los datos con un flanco descendente y SO captura los datos con un borde ascendente

- No hay ninguna señal de START o STOP para las tramas, hay un Chip Select (CS)

- Velocidad: 1 70 Mbps

http://dte.uc3m.es

Figura: https://www.slideserve.com/neveah/spi

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

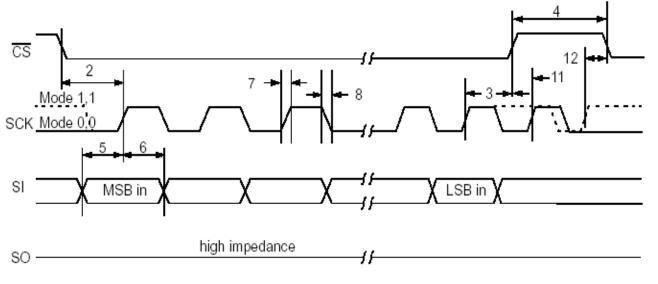

### **SPI: Funcionamiento Maestro -> Esclavo**

- Si se quiere comunicar, se ajusta CS al valor "0", se transmite y se ajusta CS al valor "1" cuando se quiera terminar la transmisión

- No hay especificaciones para la longitud de los datos, puede ser de 8 bits o no

- Los datos son validados con flancos en la línea SCK (recuerda que en l<sup>2</sup>C es con SCL = "1")

http://dte.uc3m.es

Figura 1: Archivo "25AA040/25LC040/25C040 - Product data sheet", 1997, Pag. 4 Figura 2: https://www.slideserve.com/neveah/spi

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

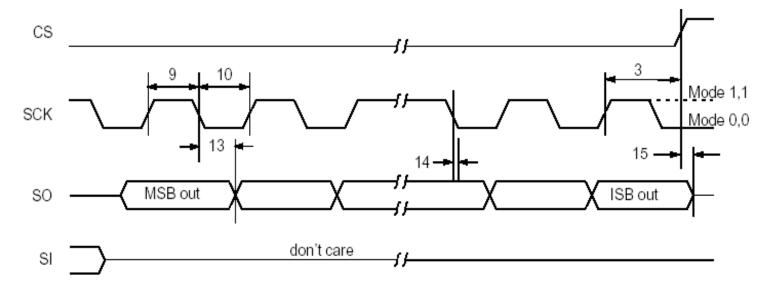

## **SPI: Funcionamiento Esclavo -> Maestro**

- Si se quiere comunicar, se ajusta CS al valor "0", se transmite y se ajusta CS al valor "1" cuando se quiera terminar la transmisión

- No hay especificaciones para la longitud de los datos, puede ser de 8 bits o no.

- Los datos son validados con flancos en la línea SCK (recuerda que en l<sup>2</sup>C es con SCL = "1")

http://dte.uc3m.es

Figura 1: Archivo "25AA040/25LC040/25C040 - Product data sheet", 1997, Pag. 4

Figura 2: https://www.slideserve.com/neveah/spi

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

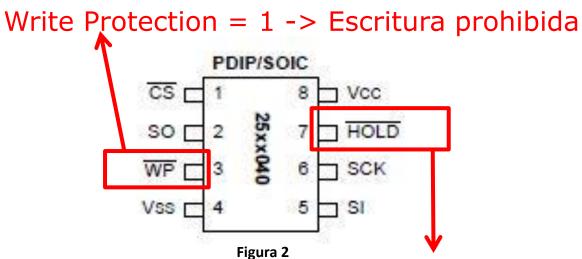

### SPI: Memoria 25AA040

Figura 1

Hold = 1 -> Memoria deshabilitada

|                | Instruction Name | Instruction Format | Description                                               |  |  |

|----------------|------------------|--------------------|-----------------------------------------------------------|--|--|

|                | READ             | 0000 A8011         | Read data from memory array beginning at selected address |  |  |

|                | WRITE            | 0000 A8010         | Write data to memory array beginning at selected address  |  |  |

|                | WRDI             | 0000 0100          | Reset the write enable latch (disable write operations)   |  |  |

|                | WREN 0000 0110   |                    | Set the write enable latch (enable write operations)      |  |  |

|                | RDSR 0000 0101   |                    | Read status register                                      |  |  |

| WRSR 0000 0001 |                  | 0000 0001          | Write status register                                     |  |  |

Figura 1: https://www.microchip.com/wwwproducts/en/25AA040

Figura 2: Archivo "25AA040/25LC040/25C040 - Product data sheet", 1997, Pag. 1

Figura 3: Archivo "25AA040/25LC040/25C040 - Product data sheet", 1997, Pag. 6

Figura 4: https://www.slideserve.com/neveah/spi

Figura 3

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

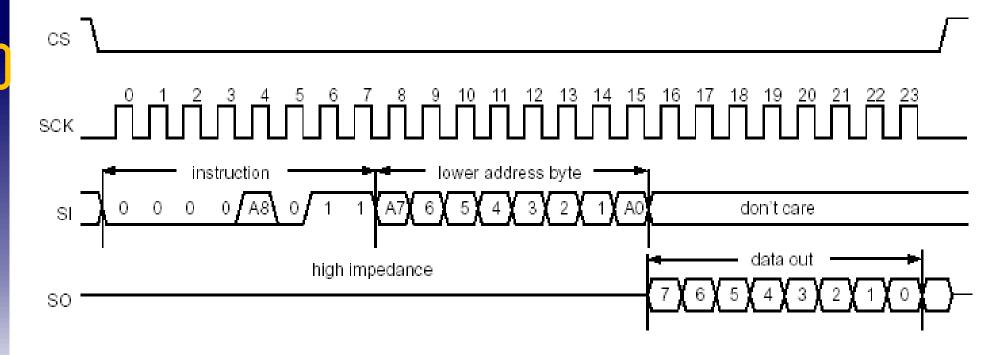

### SPI: Memoria 25AA040 - Instrucción READ

Ahora existe una instrucción de lectura, no como en l<sup>2</sup>C en la que era necesario hacer un truco para leer los datos

Figura 1

http://dte.uc3m.es

Figura 1: Archivo "25AA040/25LC040/25C040 - Product data sheet", 1997, Pag. 7

Figura 2: https://www.slideserve.com/neveah/spi

- 1. Conceptos principales

- 2. I<sup>2</sup>C

- 3. SPI

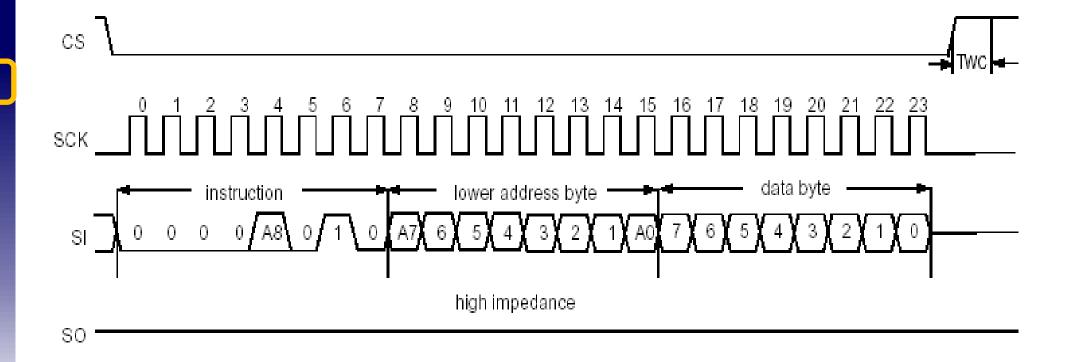

### SPI: Memoria 25AA040 - Instrucción WRITE

También existe una instrucción de escritura

Figura 1

http://dte.uc3m.es

Figura 1: Archivo "25AA040/25LC040/25C040 - Product data sheet", 1997, Pag. 7 Figura 2: https://www.slideserve.com/neveah/spi